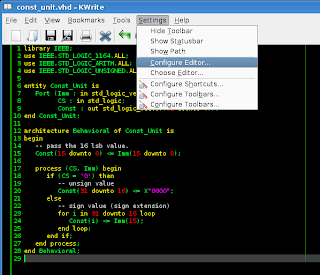

- open your code using kwrite and set the highlighting color as your flavor by selecting "Settings > Configure Editor..." and clicking on "Fonts & Colors"

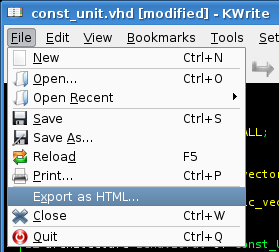

- export your code into html file by clicking on "File > Export as HTML..." and "Save"

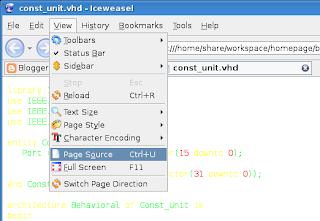

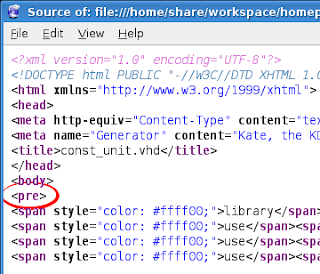

- copy the html source of your html file by opening your html file with your internet browser and clicking on "View > Page Source" (if you are using mozilla firefox). copy from tag <pre> to </pre>.

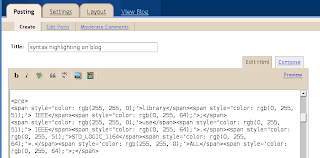

- paste it into your new posting blog in side "Edit Html" tab box and click back on "Compose" tab box to see the result.

- add border to make it beautiful by changing html tag <pre> with following settings.

<pre style="border: 1px dashed rgb(64, 64, 64); margin: 0em; padding: 1em; overflow: auto; background-color: rgb(0, 0, 0);">

- done! following examples of highlighted vhdl and verilog code

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity Const_Unit is

Port (Imm : in std_logic_vector(15 downto 0);

CS : in std_logic;

Const : out std_logic_vector(31 downto 0));

end Const_Unit;

architecture Behavioral of Const_Unit is

begin

-- pass the 16 lsb value.

Const(15 downto 0) <= Imm(15 downto 0);

process (CS, Imm) begin

if (CS = '0') then

-- unsign value

Const(31 downto 16) <= X"0000";

else

-- sign value (sign extension)

for i in 31 downto 16 loop

Const(i) <= Imm(15);

end loop;

end if;

end process;

end Behavioral;

code: highlighted vhdl code

`timescale 1ns / 1ns

`include "../inc/ctr.h"

module ctr(

// input

clk, rst,

// output

out

);

// i/os

input clk, // clock

rst; // reset

output [`WIDTH-1:0] out; // output

// internal signals

wire clk, // clock

rst; // reset

reg [`WIDTH-1:0] out; // output

always @(posedge clk or posedge rst) begin

if (rst)

out <= 0;

else

out <= out + 1;

end

endmodule

code: highlighted verilog code

No comments:

Post a Comment